KUPEGA Hearing Aid SoC

KUPEGA Hearing Aid SoC

KUPEGA Hearing Aid SoC

- Initial Tape-out

- 2024

Involved Chipdesign Germany Members

Description

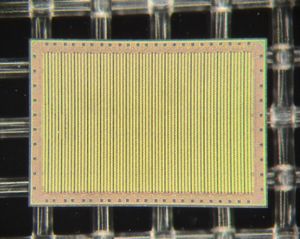

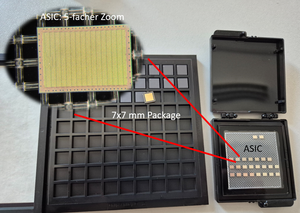

The Lightweight Interleaver Network Accelerator (LINA) is an ultra-low-power neural network accelerator designed for real-time audio processing on the KUPEGA Hearing Aid SoC. It efficiently executes 2D convolution, the fundamental operation of convolutional, fully connected, and recurrent neural networks. A flexible interleaver network dynamically partitions workloads between memory and up to 128 processing elements to maximize utilization while minimizing data movement. Fabricated in 22 nm FD-SOI, the ASIC achieves up to 7339 GMACs/s/mW. Measurements demonstrate 6.1 million MACs in 1.6 ms at 54 MHz and 4.97 mW at extended processing time.

Technical Specifications

- Die Area

- 6 mm²

- Transistors

- 2200000

- Memory Blocks

- SRAM (1.3 MiB)

- Power Consumption

- typ. 5 mW

- Supply Voltages

- 0.5V, 0.65V, 0.8V, 1.8V

- Packaging

- QFN48

- Temperature Range

- -40 °C bis +125 °C

Architecture Details

- Clock Frequency

- 50 MHz

Funding & Project Context

- Project

- Hearing4all 2.0

- Funder

- DFG

- Grant ID

390895286- Runtime

- 2023-2025

EDA Tools Used

- Cadence Virtuoso (Analog Schematic & Layout)

- Cadence Genus (Digital Synthese)

- Cadence Innovus (Digital Place & Route)

- ModelSim (Simulation)

- Vivado (Emulation)

Verification Methods

- Simulation

- FPGA-Prototyping

- Post-Silicon-Bring-up

Project Partners

The information displayed on this page has been provided by the listed Chipdesign Germany members and has not been verified by Chipdesign Germany.