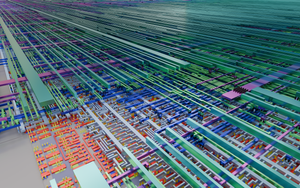

IMS Arcade SoC Rendering

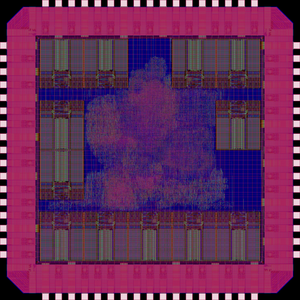

IMS Arcade SoC

IMS Arcade SoC

- Initial Tape-out

- 2025

Involved Chipdesign Germany Members

Description

The IMS-Arcade demonstrator is a RISC-V based SoC designed for a graduate lab on digital chip design. It integrates student-developed modifications to explore collaborative SoC development for a handheld gaming device. The ASIC features a custom instruction set with special SIMD instructions for audio and graphics processing. Fabricated as an experimental run in GF180MCU technology, this project tested the public PDK for the first time using Synopsys tools. The chip provides a hands-on platform for demonstrating design extensions and experimenting with interactive audio and graphics within an academic environment.

Technical Specifications

- Die Area

- 9 mm²

- Transistors

- 328904

- Memory Blocks

- SRAM (6 KiB)

- Power Consumption

- Supply Voltages

- 1.8 - 5V

- Packaging

- QFN64

- Temperature Range

- -40 °C bis +125 °C

Architecture Details

- ISA

- RISC-V RV32IMCB

- Cores

- 1

- Clock Frequency

- 32 MHz

- Pipeline Stages

- 2

- Memory Interface

- OBI

EDA Tools Used

- Synopsys Fusion Compiler (RTL to GDSII Flow)

- Synopsys VCS (RTL and Gate-Level Simulation)

- Synopsys ICV (DRC and Metal Fill)

- KLayout (DRC)

- Vivado (Emulation)

Verification Methods

- Simulation

- FPGA-Prototyping

Project Partners

The information displayed on this page has been provided by the listed Chipdesign Germany members and has not been verified by Chipdesign Germany.