Die

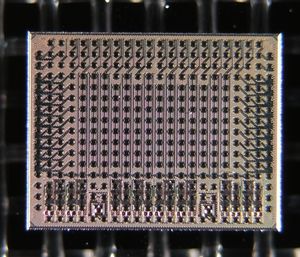

ASIC layout

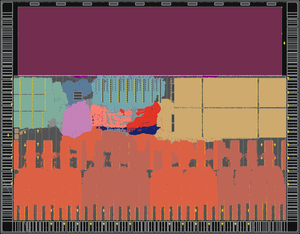

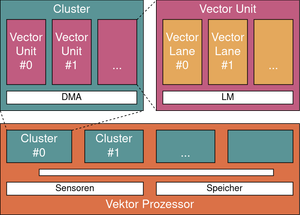

V2PRO architecture

ANAKONDA (ZuSE-KI-AVF)

- Initial Tape-out

- 2025

Involved Chipdesign Germany Members

Description

Modern and future AI-based automotive applications, such as autonomous driving, require the efficient real-time processing of huge amounts of data from different sensors, like camera, radar, and LiDAR. In the ZuSE-KI-AVF project, multiple university, and industry partners collaborate to develop a novel massive parallel processor architecture, based on a cus-tomized RISC-V host processor, and an efficient high-performance vertical vector coprocessor. In addition, a software development framework is also provided to efficiently program AI-based sensor processing applications. The proposed processor system was verified and evaluated on a state-of-the-art UltraScale+ FPGA board, reaching a processing performance of up to 126.9 FPS, while executing the YOLO-LITE CNN on 224x224 input images. Further optimizations of the FPGA design and the realization of the processor system on a 22nm FDSOI CMOS technology are planned. [Thieu et.al.]

Technical Specifications

- Die Area

- 9 mm²

- Interfaces

- SPI, UART, GPIO, AXI4 via STAB, 64bit parallel bus

Architecture Details

- ISA

- V2PRO

- Cores

- 4

- Clock Frequency

- 1500 MHz

Process & Development

- Foundry

- GlobalFoundries

Funding & Project Context

- Project

- ZuSE-KI-AVF

- Funder

- BMBF

- Grant ID

16ME0379- Runtime

- 2022-2025

Licenses

- IP Blocks (own)

- V2PRO coprocessor

- IP Blocks (3rd party)

- 16Gbit/s SerDes

EDA Tools Used

- Cadence Genus (Synthesis)

- Cadence Innovous (Place & Route)

Verification Methods

- Simulation

- FPGA-Prototyping (Zynq UltraScale+)

Project Partners

- Institute of Microelectronic Systems, Leibniz University Hannover

- Dream Chip Technologies GmbH

- Robert Bosch GmbH

- Cadence Design Systems GmbH

- Institute for Communication Technologies and Embedded Systems (RWTH Aachen)

- Division of Microelectronic Systems Design (RPTU)

- Chair for Chip Design for Embedded Computing (TU Braunschweig)

The information displayed on this page has been provided by the listed Chipdesign Germany members and has not been verified by Chipdesign Germany.