KUPEGA Hearing Aid SoC

KUPEGA Hearing Aid SoC

KUPEGA Hearing Aid SoC

- Initiales Tape-out

- 2024

Beteiligte Chipdesign Germany Mitglieder

Beschreibung

Technische Spezifikationen

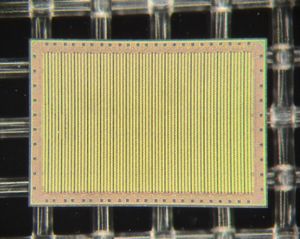

- Chipfläche

- 6 mm²

- Transistoren

- 2200000

- Speicherblöcke

- SRAM (1.3 MiB)

- Leistungsaufnahme

- typ. 5 mW

- Versorgungsspannungen

- 0.5V, 0.65V, 0.8V, 1.8V

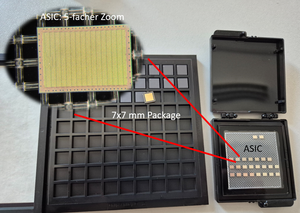

- Gehäuse

- QFN48

- Temperaturbereich

- -40 °C bis +125 °C

Architekturdetails

- Taktfrequenz

- 50 MHz

Förderung & Projektkontext

- Projekt

- Hearing4all 2.0

- Förderer

- DFG

- Förderkennzeichen

390895286- Laufzeit

- 2023-2025

Verwendete EDA-Tools

- Cadence Virtuoso (Analog Schematic & Layout)

- Cadence Genus (Digital Synthese)

- Cadence Innovus (Digital Place & Route)

- ModelSim (Simulation)

- Vivado (Emulation)

Verifikationsmethoden

- Simulation

- FPGA-Prototyping

- Post-Silicon-Bring-up

Die auf dieser Seite angezeigten Informationen wurden von den genannten Chipdesign Germany-Mitgliedern bereitgestellt und sind von Chipdesign Germany nicht überprüft worden.