Die

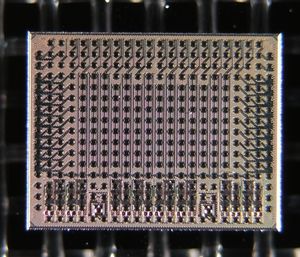

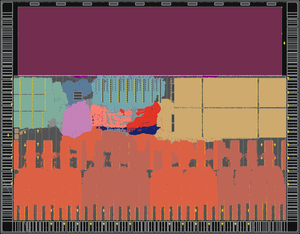

ASIC Layout

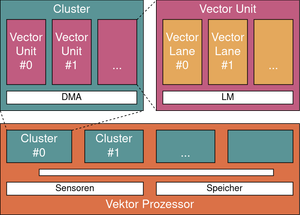

V2PRO Architektur

ANAKONDA (ZuSE-KI-AVF)

- Initiales Tape-out

- 2025

Beteiligte Chipdesign Germany Mitglieder

Beschreibung

Technische Spezifikationen

- Chipfläche

- 9 mm²

- Schnittstellen

- SPI, UART, GPIO, AXI4 via STAB, 64bit parallel bus

Architekturdetails

- ISA

- V2PRO

- Kerne

- 4

- Taktfrequenz

- 1500 MHz

Prozess & Entwicklung

- Foundry

- GlobalFoundries

Förderung & Projektkontext

- Projekt

- ZuSE-KI-AVF

- Förderer

- BMBF

- Förderkennzeichen

16ME0379- Laufzeit

- 2022-2025

Lizenzen

- IP-Blöcke (own)

- V2PRO coprocessor

- IP-Blöcke (3rd party)

- 16Gbit/s SerDes

Verwendete EDA-Tools

- Cadence Genus (Synthesis)

- Cadence Innovous (Place & Route)

Verifikationsmethoden

- Simulation

- FPGA-Prototyping (Zynq UltraScale+)

Projektpartner

- Institut für Mikroelektronische Systeme, Leibniz Universität Hannover

- Dream Chip Technologies GmbH

- Robert Bosch GmbH

- Cadence Design Systems GmbH

- Institut für Kommunikationstechnologien und eingebettete Systeme (RWTH Aachen)

- Fachgebiet Entwurf Mikroelektronischer Systeme (RPTU)

- Chair for Chip Design for Embedded Computing (TU Braunschweig)

Die auf dieser Seite angezeigten Informationen wurden von den genannten Chipdesign Germany-Mitgliedern bereitgestellt und sind von Chipdesign Germany nicht überprüft worden.